PCB设计过程中如何考虑阻抗控制和叠层设计?

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。6 [+ n4 @% G8 M: t* Z

: j" s: u% W( T- p- Z

阻抗控制* F4 W) {) w" y, J/ P

5 x# Z7 Z, A) A

阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB 阻抗的范围是 25 至120 欧姆。* N6 ^' A+ o6 l& b

7 G4 B, F: O, } ]) x l

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。迹线和板层构成了控制阻抗。PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:

信号迹线的宽度和厚度

迹线两侧的内核或预填材质的高度

/ R8 q5 N }" h8 R" H7 `8 D4 B9 y, N* |

迹线和板层的配置

. f6 H/ A- F2 M7 m, B# k

内核和预填材质的绝缘常数

% W0 m# d( s% F' J6 k0 D+ o; J

PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。, ^/ s: _; t- K& M

微带线(Microstrip):& b( [9 H9 b M" q: i

" w4 ~+ ?1 _7 B

微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。( b1 `0 @7 X3 Q! n$ m, b

! B$ j9 l" ^$ Z& D2 y- x' I

带状线(Stripline):

带状线是置于两个参考平面之间的带状导线,电介质的介电常数可以不同。具体的微带线和带状线有很多种,如覆膜微带线等,都是跟具体的PCB的叠层结构相关。& g" _4 E; s4 V6 f) c

7 T9 k5 ]3 H$ a

用于计算特性阻抗的等式需要复杂的数学计算,通常使用场求解方法,其中包括边界元素分析在内,因此使用专门的阻抗计算软件SI9000,我们所需做的就是控制特性阻抗的参数:

对于W1、W2的说明:' ]4 t- _% K( ^/ ]9 E9 Z- m

计算值必须在红框范围内。其余情况类推。

; m+ q6 I& }+ C" e9 ~. E3 T/ e

下面利用SI9000计算是否达到阻抗控制的要求:$ z4 w6 e6 y& d# A, ~. k" Y3 L2 z4 `

首先计算DDR数据线的单端阻抗控制:

% y2 w, h3 h1 T) `0 d

TOP层:铜厚为0.5OZ,走线宽度为5MIL,距参考平面的距离为3.8MIL,介电常数为4.2。选择模型,代入参数,选择lossless calculation,如图所示:

5 f0 o3 u; U& V5 w/ _- }# x

coating表示涂覆层,如果没有涂覆层,就在thickness 中填0,dielectric(介电常数)填1(空气)。

substrate表示基板层,即电介质层,一般采用FR-4,厚度是通过阻抗计算软件计算得到,介电常数为4.2(频率小于1GHz时)。

: \7 m- K4 @, B) T- Y' Z. {

点击Weight(oz)项,可以设定铺铜的铜厚,铜厚决定了走线的厚度。6 O+ H* |* E' t5 p x$ P, G6 ]

9、绝缘层的Prepreg/Core的概念:

PP(prepreg)是种介质材料,由玻璃纤维和环氧树脂组成,core其实也是PP类型介质,只不过他的两面都覆有铜箔,而PP没有,制作多层板时,通常将CORE和PP配合使用,CORE与CORE之间用PP粘合。' l6 L( D0 Z' p) y

+ k. O) Q" @! V! V# [$ p0 z# t

10、PCB叠层设计中的注意事项:

; | k: l8 A# K# \

(1)、翘曲问题/ l/ L6 c; D( C) T1 j+ X' K2 M

" ^/ u7 H+ u5 I

PCB的叠层设计要保持对称,即各层的介质层厚、铺铜厚度上下对称,拿六层板来说,就是TOP-GND与BOTTOM-POWER的介质厚度和铜厚一致,GND-L2与L3-POWER的介质厚度和铜厚一致。这样在层压的时候不会出现翘曲。$ ]0 R4 E C* V+ v; y* ]% b

(2)、信号层应该和邻近的参考平面紧密耦合(即信号层和邻近敷铜层之间的介质厚度要很小);电源敷铜和地敷铜应该紧密耦合。

0 V! P, e, g8 j( w. B8 {

(3)、在很高速的情况下,可以加入多余的地层来隔离信号层,但建议不要多家电源层来隔离,这样可能造成不必要的噪声干扰。/ K% R6 r: G/ V7 _2 `

" O! O- K0 y$ D' [/ K1 s5 [" r

(4)、层的排布一般原则:+ f% J+ m8 l7 d1 ?5 \

元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

所有信号层尽可能与地平面相邻;

尽量避免两信号层直接相邻;8 q @& b0 M3 R2 C( c! H

0 y! c) W* A( S

主电源尽可能与其对应地相邻;

1 c4 e0 O# a6 \5 V

兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ 以上的

* D( Y9 O8 Y% c+ R( ~

(50MHZ 以下的情况可参照,适当放宽),建议排布原则:* u0 G/ _. E! K3 |

元件面、焊接面为完整的地平面(屏蔽);

, X: C/ ~7 W3 M: ~( `7 l

无相邻平行布线层;, @# W3 H5 C1 e( ~( t

所有信号层尽可能与地平面相邻;

关键信号与地层相邻,不跨分割区。

: j" s: u% W( T- p- Z

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。印制电路板上导线的特性阻抗是电路板设计的一个重要指标,特别是在高频电 路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

阻抗控制* F4 W) {) w" y, J/ P

5 x# Z7 Z, A) A

阻抗控制(eImpedance Controling),线路板中的导体中会有各种信号的传递,为提高其传输速率而必须提高其频率,线路本身若因蚀刻,叠层厚度,导线宽度等不同因素,将会造成阻抗值得变化,使其信号失真。故在高速线路板上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。

PCB 迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB 阻抗的范围是 25 至120 欧姆。* N6 ^' A+ o6 l& b

7 G4 B, F: O, } ]) x l

在实际情况下,PCB 传输线路通常由一个导线迹线、一个或多个参考层和绝缘材质组成。迹线和板层构成了控制阻抗。PCB 将常常采用多层结构,并且控制阻抗也可以采用各种方式来构建。但是,无论使用什么方式,阻抗值都将由其物理结构和绝缘材料的电子特性决定:

信号迹线的宽度和厚度

迹线两侧的内核或预填材质的高度

/ R8 q5 N }" h8 R" H7 `8 D4 B9 y, N* |

迹线和板层的配置

. f6 H/ A- F2 M7 m, B# k

内核和预填材质的绝缘常数

% W0 m# d( s% F' J6 k0 D+ o; J

PCB传输线主要有两种形式:微带线(Microstrip)与带状线(Stripline)。, ^/ s: _; t- K& M

微带线(Microstrip):& b( [9 H9 b M" q: i

" w4 ~+ ?1 _7 B

微带线是一根带状导线,指只有一边存在参考平面的传输线,顶部和侧边都曝置于空气中(也可上敷涂覆层),位于绝缘常数 Er 线路板的表面之上,以电源或接地层为参考。( b1 `0 @7 X3 Q! n$ m, b

! B$ j9 l" ^$ Z& D2 y- x' I

带状线(Stripline):

带状线是置于两个参考平面之间的带状导线,电介质的介电常数可以不同。具体的微带线和带状线有很多种,如覆膜微带线等,都是跟具体的PCB的叠层结构相关。& g" _4 E; s4 V6 f) c

7 T9 k5 ]3 H$ a

用于计算特性阻抗的等式需要复杂的数学计算,通常使用场求解方法,其中包括边界元素分析在内,因此使用专门的阻抗计算软件SI9000,我们所需做的就是控制特性阻抗的参数:

绝缘层的介电常数Er、走线宽度W1、W2(梯形)、走线厚度T和绝缘层厚度H。8 v

A3 J, O6 B s) o S" E/ t

A3 J, O6 B s) o S" E/ t

对于W1、W2的说明:' ]4 t- _% K( ^/ ]9 E9 Z- m

计算值必须在红框范围内。其余情况类推。

; m+ q6 I& }+ C" e9 ~. E3 T/ e

下面利用SI9000计算是否达到阻抗控制的要求:$ z4 w6 e6 y& d# A, ~. k" Y3 L2 z4 `

首先计算DDR数据线的单端阻抗控制:

% y2 w, h3 h1 T) `0 d

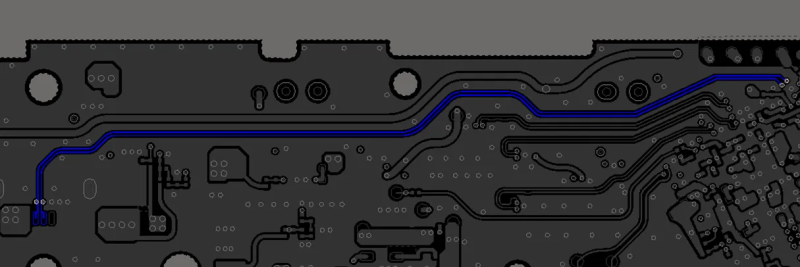

TOP层:铜厚为0.5OZ,走线宽度为5MIL,距参考平面的距离为3.8MIL,介电常数为4.2。选择模型,代入参数,选择lossless calculation,如图所示:

5 f0 o3 u; U& V5 w/ _- }# x

coating表示涂覆层,如果没有涂覆层,就在thickness 中填0,dielectric(介电常数)填1(空气)。

substrate表示基板层,即电介质层,一般采用FR-4,厚度是通过阻抗计算软件计算得到,介电常数为4.2(频率小于1GHz时)。

: \7 m- K4 @, B) T- Y' Z. {

点击Weight(oz)项,可以设定铺铜的铜厚,铜厚决定了走线的厚度。6 O+ H* |* E' t5 p x$ P, G6 ]

9、绝缘层的Prepreg/Core的概念:

PP(prepreg)是种介质材料,由玻璃纤维和环氧树脂组成,core其实也是PP类型介质,只不过他的两面都覆有铜箔,而PP没有,制作多层板时,通常将CORE和PP配合使用,CORE与CORE之间用PP粘合。' l6 L( D0 Z' p) y

+ k. O) Q" @! V! V# [$ p0 z# t

10、PCB叠层设计中的注意事项:

; | k: l8 A# K# \

(1)、翘曲问题/ l/ L6 c; D( C) T1 j+ X' K2 M

" ^/ u7 H+ u5 I

PCB的叠层设计要保持对称,即各层的介质层厚、铺铜厚度上下对称,拿六层板来说,就是TOP-GND与BOTTOM-POWER的介质厚度和铜厚一致,GND-L2与L3-POWER的介质厚度和铜厚一致。这样在层压的时候不会出现翘曲。$ ]0 R4 E C* V+ v; y* ]% b

(2)、信号层应该和邻近的参考平面紧密耦合(即信号层和邻近敷铜层之间的介质厚度要很小);电源敷铜和地敷铜应该紧密耦合。

0 V! P, e, g8 j( w. B8 {

(3)、在很高速的情况下,可以加入多余的地层来隔离信号层,但建议不要多家电源层来隔离,这样可能造成不必要的噪声干扰。/ K% R6 r: G/ V7 _2 `

" O! O- K0 y$ D' [/ K1 s5 [" r

(4)、层的排布一般原则:+ f% J+ m8 l7 d1 ?5 \

元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;

所有信号层尽可能与地平面相邻;

尽量避免两信号层直接相邻;8 q @& b0 M3 R2 C( c! H

0 y! c) W* A( S

主电源尽可能与其对应地相邻;

1 c4 e0 O# a6 \5 V

兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在50MHZ 以上的

* D( Y9 O8 Y% c+ R( ~

(50MHZ 以下的情况可参照,适当放宽),建议排布原则:* u0 G/ _. E! K3 |

元件面、焊接面为完整的地平面(屏蔽);

, X: C/ ~7 W3 M: ~( `7 l

无相邻平行布线层;, @# W3 H5 C1 e( ~( t

所有信号层尽可能与地平面相邻;

关键信号与地层相邻,不跨分割区。

- smt贴片机厂家2024-10-30

- smt贴片dgp(SMT贴片技术在现代电子制造中的具体应用有哪些?)2024-10-31

- smt贴片加工顺德2024-10-28

- smt贴片加工莲塘(莲塘SMT贴片加工企业有哪些代表性公司?)2024-10-28

- smt贴片加工乐清2024-10-28

- 广西smt贴片加工(广西SMT贴片加工行业的主要企业有哪些?)2024-10-29

- 龙岗smt贴片线2024-11-02

- smt加工贴片流水(SMT加工贴片流水线中回流焊接的温度曲线如何控制?)2024-10-26

- SMT贴片越多越便宜吗?2025-03-28

- smt贴片真空吸2024-11-02

- PCB打样价格怎么压缩成本?| 捷创电子2025-03-24

- PCB打样报价的影响因素 | 捷创电子2025-03-24

- smt贴片定制加工(SMT贴片定制加工的最新技术发展有哪些?)2024-10-25

- smt贴片FVT2024-11-01

- 深圳PCBA加工厂推荐2025-03-26

- 深圳捷创电子第六届迎新技能大赛20232023-01-16

- PCB打样哪家速度快又不贵?| 捷创电子2025-03-24

- smt贴片加工焊点2024-10-28

- smt分段式贴片2024-11-02

- 兴化贴片smt加工2024-10-29